Wire a = x & y // Implicit assignmentĬonsider the following digital circuit made from combinational gates and the corresponding Verilog code.Ĭombinational logic requires the inputs to be continuously driven to maintain the output unlike sequential elements like flip flops where the value is captured and stored at the edge of a clock. Verilog also allows an assignment to be done when the net is declared and is called implicit assignment. When an assign statement is used to assign the given net with some value, it is called explicit assignment. reg signals can only be driven in procedural blocks like initial and always. This is because a reg variable is capable of storing data and does not require to be driven continuously. It is illegal to drive or assign reg type variables with an assign statement. Case #10: If we reverse order on LHS keeping RHS same, we get a = 'b01 and b='b0 RHS is evaluated to 11001 and LHS is 3-bit wide so first 3 bits from LSB of RHS Case #9: LHS can also be concatenated: a is 2-bit vector and b is scalar Case #8: Same variable can be used multiple times as well and z = 'b00111 Case #7: Say we explicitly assign only 3-bits of z and leave remaining unconnected are chosen from x, then z = 'b00001 because z will be driven with 0 Case #6: Partial selection of operands on RHS is also possible and say only 2-bits now it becomes unknown which will win. at the time is 0 and the second assignment where it is driven with value 1, so

with different values, where the first line is driven with the value of X which

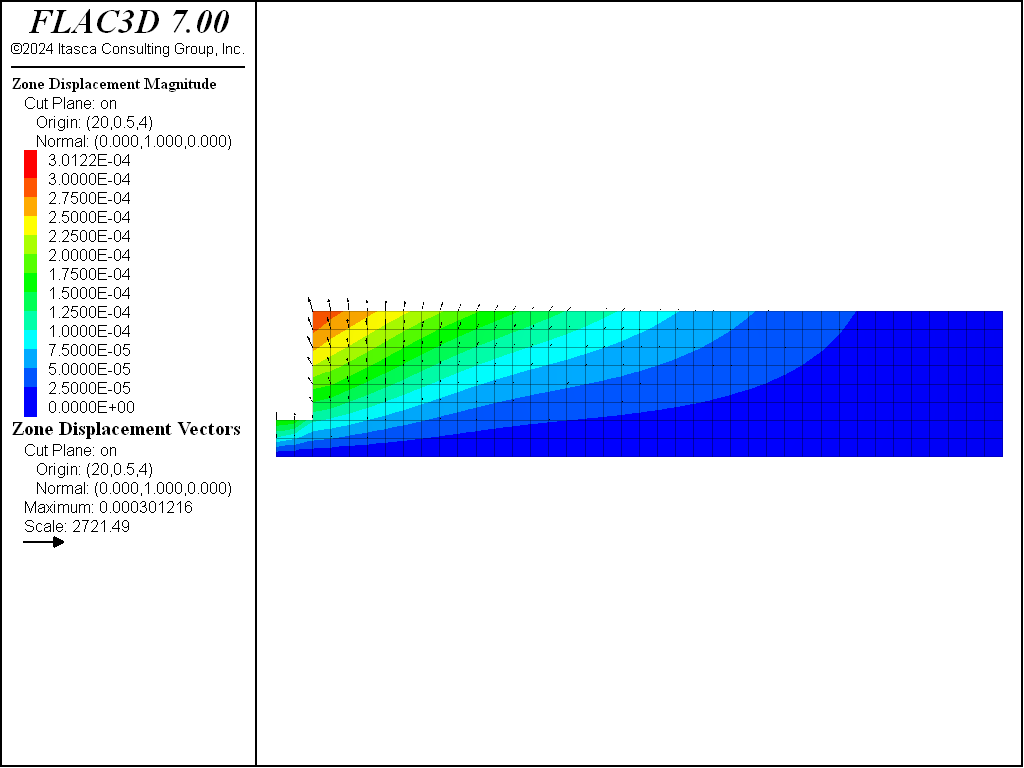

Right handed input system flac3d drivers#

Case #5: Assume bit3 is instead driven with value 1, so now there are two drivers and both are driving the same value of 0.

Case #4: Assume bit3 is driven instead, but now there are two drivers for bit3, Now z = 'b1001Z because only bit0 remains undriven Case #3: The same statement is used but now bit4 of z is driven with a constant and is assigned to selected 3-bits of net z. Case #2: 4-bits of x and 1 bit of y is concatenated to get a 5-bit net and is assigned to the 5-bit nets of z. Case #1: 4-bits of x and 1 bit of y is concatenated to get a 5-bit net If x='hC and y='h1 let us see the value of z Assume one of the following assignments are chosen in real design Module xyz (input x, // x is a 4-bit vector net

Right handed input system flac3d code#

Treat each case as the only code in the module, else many assign statements on the same signal will definitely make the output become X. The module shown below takes two inputs and uses an assign statement to drive the output z using part-select and multiple bit concatenations. If the wires are instead converted into ports and synthesized, we will get an RTL schematic like the one shown below after synthesis.Ĭontinuous assignment statement can be used to represent combinational gates in Verilog. i1 and i2 with the logical AND & form the expression. In the following example, a net called out is driven continuously by an expression of signals.

0 kommentar(er)

0 kommentar(er)